Sequential element (data_out_reg) is unused and will be removed from module linear_feedback_shift_reg.

inferring latch for variable 'polynomial_reg' inferring latch for variable 'current_state_reg' inferring latch for variable 'data_out_reg' Found unconnected internal register 'polynomial_reg' and it is trimmed from '2' to '1' bits. When I run synthesis the result is 0 LUTs, 0 FF. Next_bit = current_state Ĭurrent_state = next_bit If(reset = RESET_ACTIVE) begin // reset process Parameter CLK_ACTIVE = 1 // clk process when clk port is CLK_ACTIVE Parameter RESET_ACTIVE = 1 // reset process when reset port is RESET_ACTIVE Parameter POLYNOMIAL = 3 // 0x11 - x^2 + x + 1 Parameter INIT_STATE = 0 // initialization state when reset process Parameter REGISTER_WIDTH = 2 // width of initial and current states

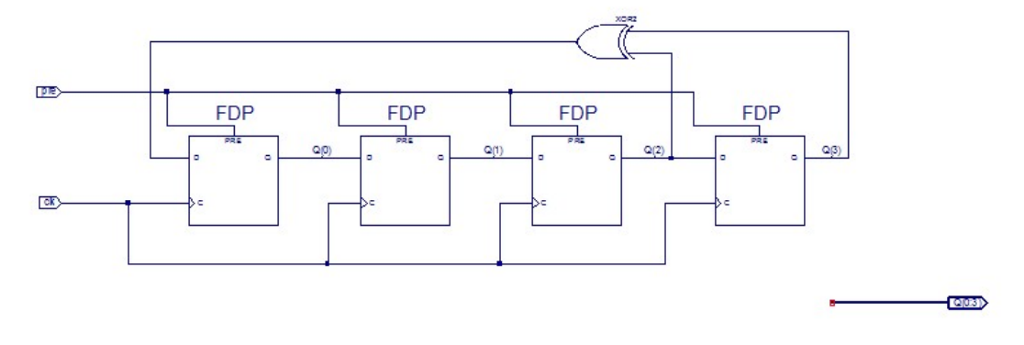

We made a small Windows utility that allows experimenting with LFSR designs.There is my module: module linear_feedback_shift_reg( clk, reset, data_out ) Wire feedback = LFSR ^ (LFSR=7'b0000000) // modified feedback allows reaching 256 states instead of 255 It is also possible to add a bit of logic in the feedback so that the LFSR reaches all possible states.

Output reg LFSR = 255 // put here the initial value The output sequence starts as follow (assuming all the flip-flops start at '1'): The one shown above is an 8-taps LFSR (it uses 8 flip-flops). Let's say you want a counter that counts more or less "randomly", you can use an LFSR.Īs you can see, an LFSR is a shift-register with some XOR gates.

0 kommentar(er)

0 kommentar(er)